先不論 Centaur 要怎樣支撐威盛那「開闢新戰場,延續高成長」的戰略大計,光從 2000 年到 2004 年,那讓人摸不著頭緒的紛亂產品時程表,就夠筆者和潛在客戶傷透腦筋了。

回顧上篇:台灣處理器拾遺》成為威盛電子 x86 處理器技術基礎的 Centaur(上)

2000 年到 2004 年的時程表大風吹

筆者不敢斬釘截鐵的確信,當初威盛花大錢,一口氣購入 Cyrix 和 Centaur,有沒有打算建構「高低檔搭配」產品線(高階 Cyrix,中低階 Centaur)的野心,或者覺得這兩間的文化是互補的。但情勢的演變,讓 Centaur 不得不面對「追求高效能」的挑戰──即使初代超純量管線的 C5X,死在 Centaur 自己的手裡。

砸了超過兩億美元進軍 x86 處理器市場的威盛,透過收購 Cyrix 而得到的 Intel P6 匯流排授權,期限只到 2006 年 5 月,2001 年 3 月 25 日讓 VIA C3 取代 Cyrix III,更等於直接把 Cyrix 品牌丟到水裡。到頭來,手上還有專利可和 Intel 討價還價的 Centaur,乍看之下,是僅剩的有價值資產。

來自威盛高層的期望,都充分反映在「產品代號充滿聖經味」的產品路線圖,「雙重產品代號(威盛的聖經人名和 Centaur 的 CxX)」也是威盛 x86 處理器的一大特色。更糟的是,這兩者還不是「一對一」的,讓產品代號與行銷名稱之間的對應關係,更顯得混亂不堪。

眼見為憑,就請各位看倌慢慢欣賞。

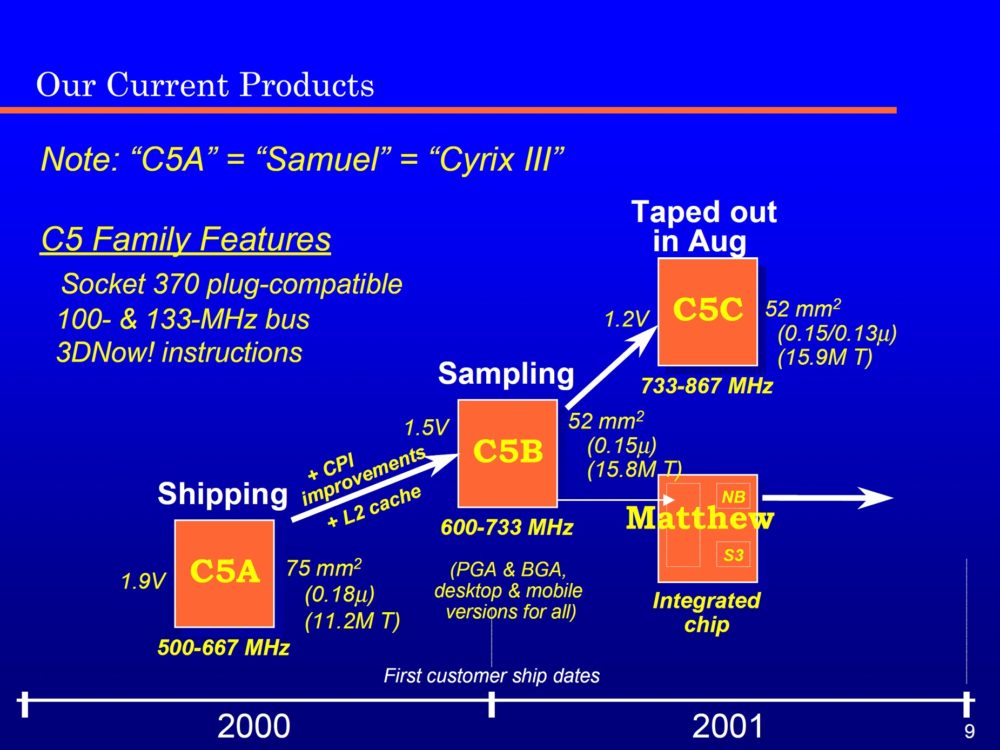

2000 年:Centaur 的首要之務是持續改進並縮小 C5 家族,並追逐 1GHz 時脈。此時簡報掛出來的品牌還叫做 VIA Cyrix。

此外,威盛在 2000 年 4 月 11 日以 3.23 億美元的代價,將 S3 繪圖晶片部門轉移至新成立的 VIA-S3 合資公司,冒出個打包威盛北橋晶片組和 S3 繪圖核心的 Matthew,實乃理所當然之事。最起碼,在當時威盛高層應認定這是市場渴望的「馬太福音」。

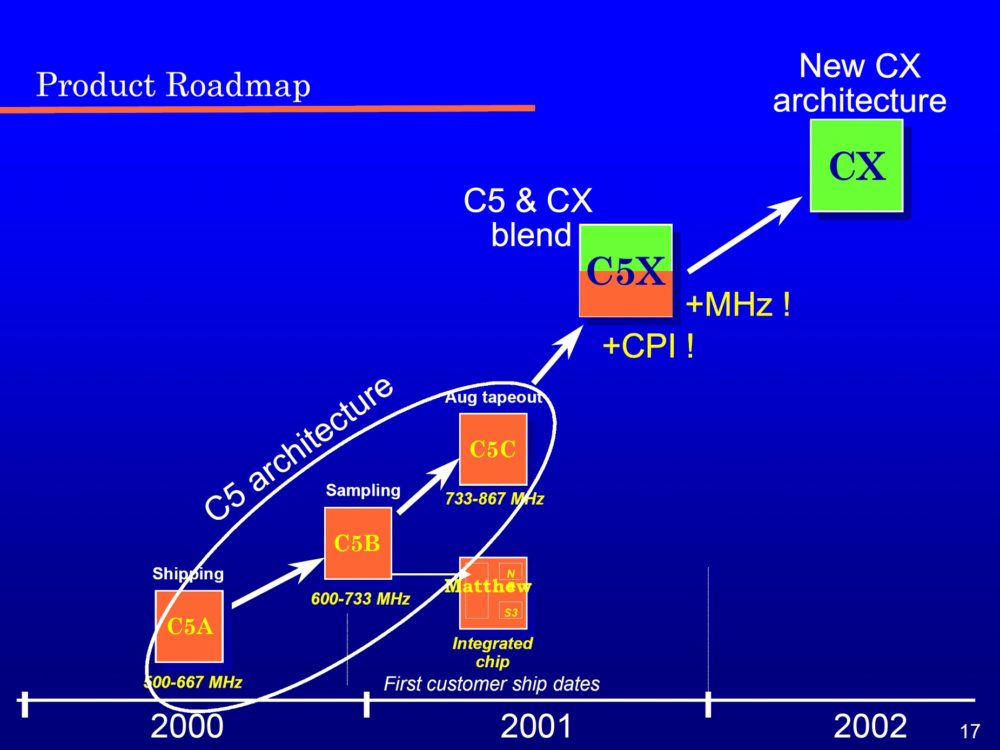

但 Centaur 有個更艱鉅的任務:在越來越熾烈的效能軍備競賽,不能再像過去一樣「裝死」。各位可回想一下,2000 年剛好是 Intel 和 AMD 爆發 1GHz 時脈爭奪戰,並點燃後來長達 20 年 x86 雙雄戰役的關鍵時刻。產品時程表出現了 Centaur 史上第一個超純量管線的 x86 處理器核心 C5X,與全新的 CX,也就是我們所熟知的 Nano。

C5X 不僅是貨真價實的超純量 x86 處理器核心,支援 SSE 指令集,更有著強大的動態分支預測、更深的指令管線與倍增的內部執行單元。當初 Centaur 沒寫在簡報內的是,為了確保可每個時脈週期擷取兩個指令,C5X 導入預先指令解碼(Pre-Decode)的指令快取記憶體,提前標定快取記憶體內的指令邊界(x86 指令集的長度並不固定),這讓實際所需容量爆增 40%。

這很顯然違背 Glenn Henry 的「信念」,也因此,預計 2001 年第三季出貨的 C5X,真的能順利誕生嗎?預估的 55 mm² 看似不大,但你怎麼猜得到威盛高層或 Glenn Henry 會吝嗇到什麼程度?更何況當「預算」超支的時候?

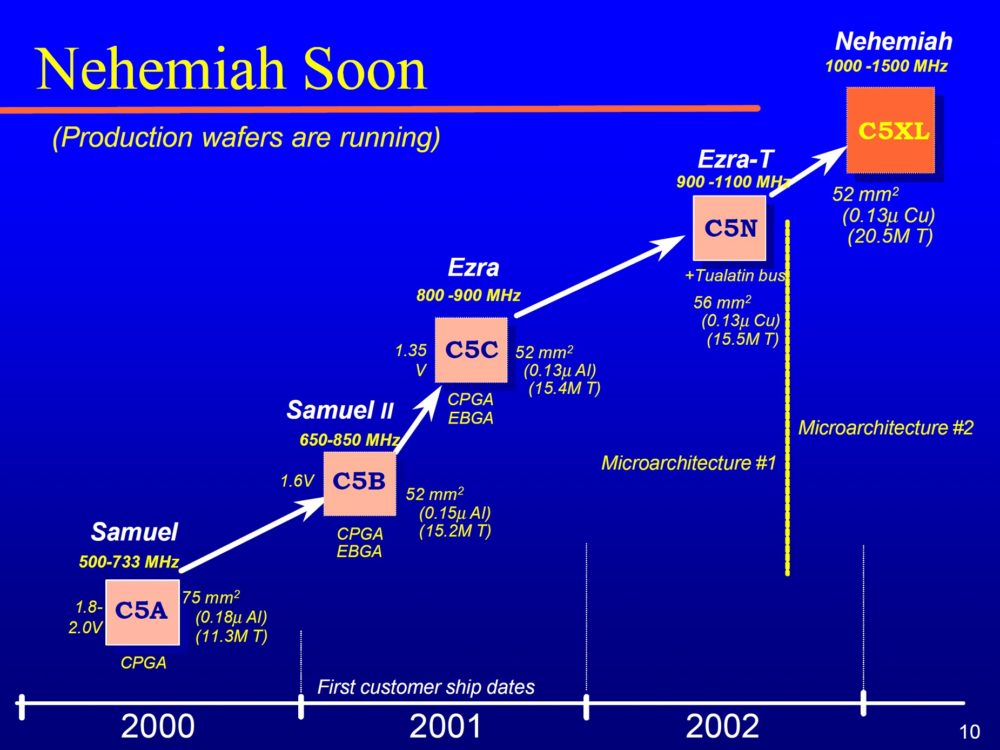

2001 年: 浮出調降電壓、壓低耗電量的 C5C「Ezra」。Cyrix 品牌也默默的消失。

Ezra-T 的那個 T 代表的是末代 Intel Pentium III「Tualatin」使用的改良版 P6 匯流排(Tualatin Bus,或稱為 P3 Bus),AGTL 電壓準位從 1.5V 調降到 1.25V,在還造成某些 Intel 晶片組的相容性問題,某些骨灰級電腦玩家應該依稀還有點印象。

C5M 僅用來進行樣品測試,真正投入量產的是 C5N。

C5X 則延後到 2002 年,還跑出來衍生款 C5XL 和 C5YL,這並不是什麼好兆頭。

全新未來架構從 CX 改名成 CZA,意義不明。

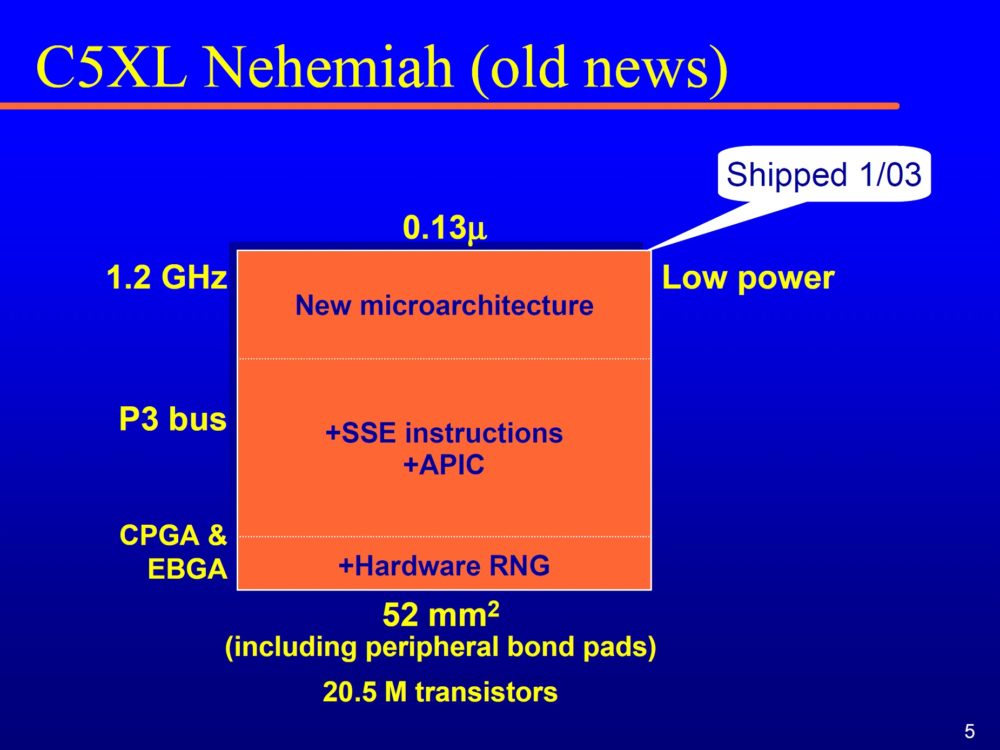

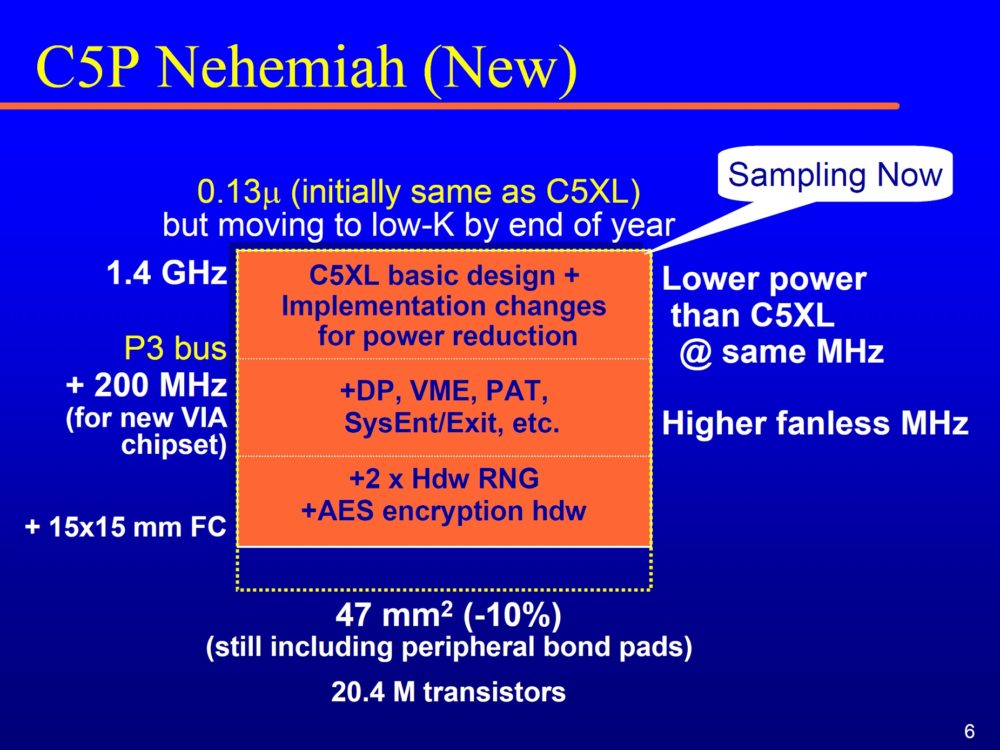

C5XL(Nehemiah)是 C5X 的砍半版本,也是 Glenn Henry 最愛的「超級純量」處理器,符合「簡單、迅速、便宜」的大原則。這時公布的 C5X 也與一年前略有出入,至少指令管線深度被縮短了,晶片面積也增肥到 78 mm²,隱隱約約讓人感受到這踩到了某個人心中的紅線。

「證實 Centaur 對簡單微架構的執著是正確的」的 C5XL,犧牲 10% 整數與 20% 多媒體效能,但減少了 30% 晶粒面積,利於提高時脈,降低耗電,而且 C5X「更貴更熱」。

2002 年:既然有了便宜的 C5XL,做為「先導研究案」的 C5X 就沒存在的必要了,Centaur 首款超純量管線 x86 處理器,就此胎死腹中。

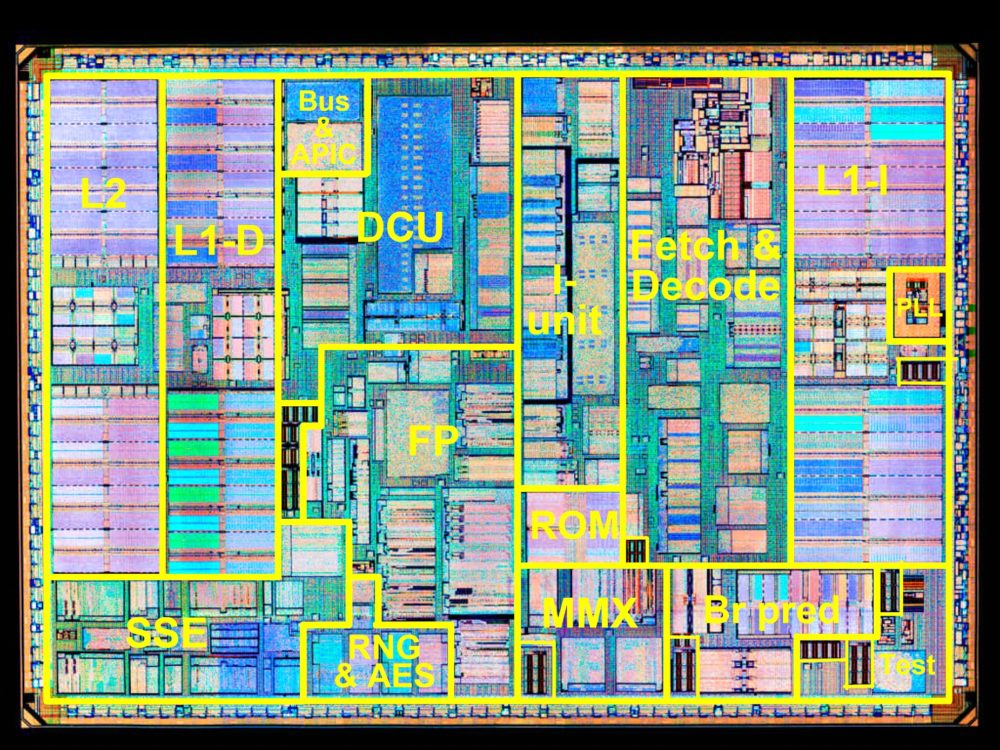

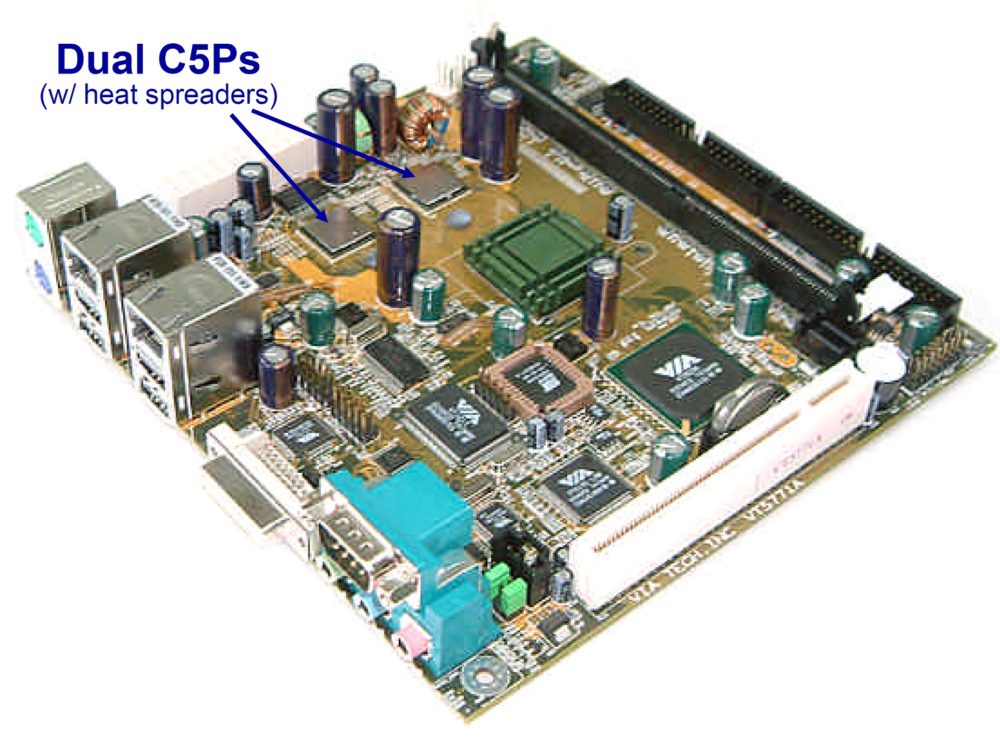

但 C5XL 並非一團糟,相較於 C5N,在相同製程,C5XL 的面積更小,時脈更高,支援 SSE 指令集。讓人眼睛一亮的是,C5XL 具備了多處理器環境必備的先進可程式化中斷控制器(APIC),這讓 C5XL 可實作雙處理器組態,但這張支票到了 C5XL 的下一版 C5P 才兌現。

C5XL 有一點值得大書特書:浮點運算不再只跑一半時脈,真是可喜可賀。

不過,以 C5XL 做為全新起點的演進圖,卻更讓人感到一頭霧水。一個 C5X 被腰斬的前車之鑑擺在眼前,誰敢保證產品時程表上的代號,有幾個可以苟活?更何況,給客戶看因「比電晶體更厲害的謀略」而隨時大風吹的產品時程表,對經營事業與開發客戶,真的妥當嗎?

千萬不要改改 roadmap 沒什麼大不了,對 Intel 和 AMD 來說,一旦爆發這種大事,一堆人都要準備去「找頭路」了。

偏偏這又是不少台商甚少意識到的壞習慣,自己關起門來「精雕細琢,近乎苛求」是一回事,改來改去(搞不好還改上癮了)的「Roadmap」往往是客戶規劃產品時的大災難。「先當個簡報王,等有客戶被騙上鉤再開案」確實是常見的業務開發技倆,但這招玩久了,只會讓自己徹底信用破產。此類英勇事蹟,在業界可謂班班可考。

全新未來微架構又從 CZA 改名成 CN,意義依舊不明。

再跑出來多出 SSE2 指令集、強化動態分支預測的 C5Z。第一時間先問:它活得下去嗎?

那個看起來很像「試水溫」的 C5Y(疑似系統匯流排換成 VIA V4 Bus)和 C5XP(C5XL 的低耗電版),似乎也很危險。那顆不存在的 C5XL/Z 的系統單晶片,就假裝沒看到好了。

2003 年:威盛開始以市場區隔細分品牌:VIA C3 入門桌機、Antaur 筆電、Eden 嵌入式應用,繼續大混亂中。

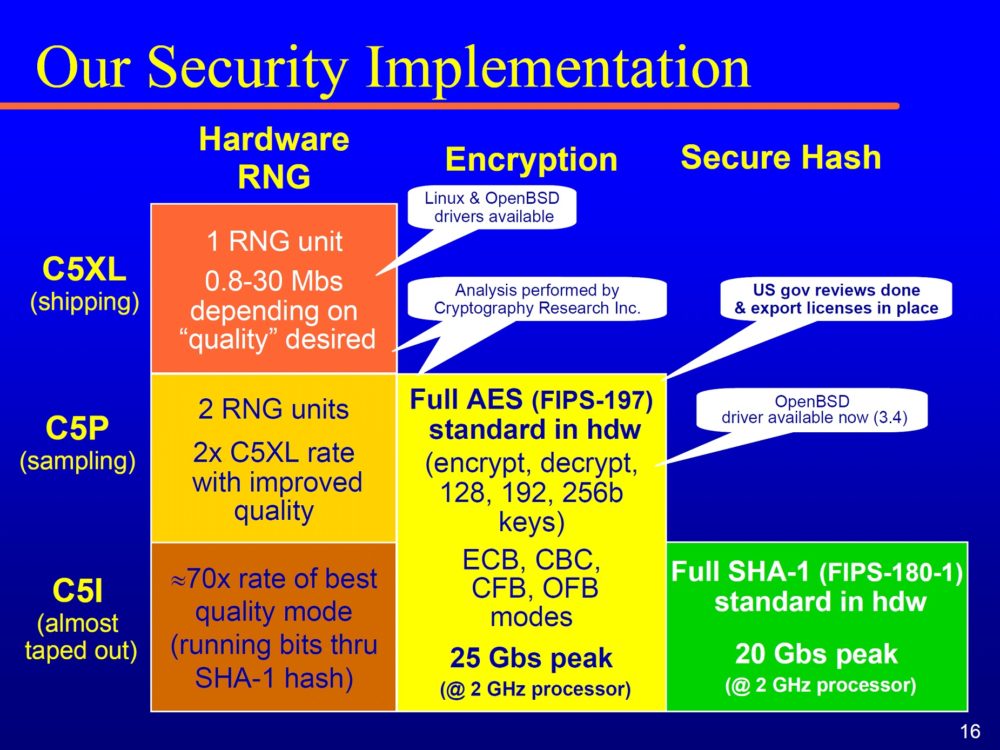

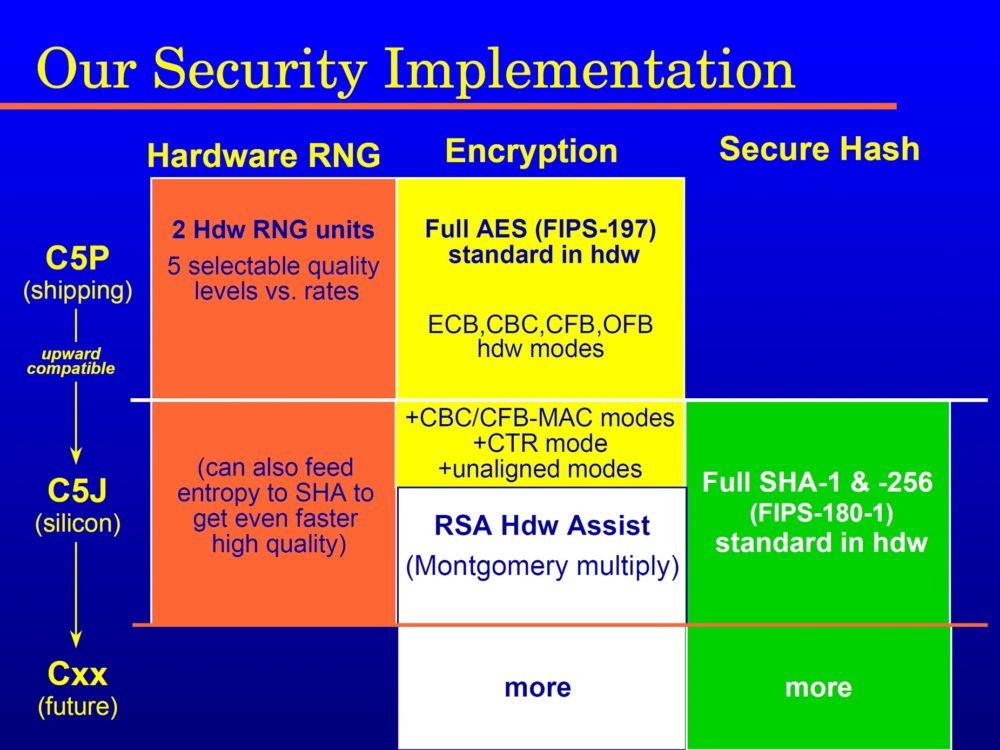

這提到了之前沒講到的 C5XL 的硬體亂數產生器(RNG,Random Number Generator),看來威盛想從資訊安全應用發掘一些獨特的利基點。

又跑出來 C5XL 的微幅改良版 C5P,在「例行公事」降低耗電、縮減面積、提昇系統匯流排之外,擴增本來該在 C5XL 就給的雙處理器組態(DP)、虛擬化(VME)、分頁位址屬性表(PAT)、硬體亂數產生器(RNG)、和硬體 AES 解密等。但對 Centaur 和 Glenn Henry,減少 10% 晶片面積才是重中之重,就為了「簡單、迅速、便宜」。

雙 C5P 處理器看起來很威,但是威盛有信心兩顆打得過人家 Intel AMD 的一顆嗎?

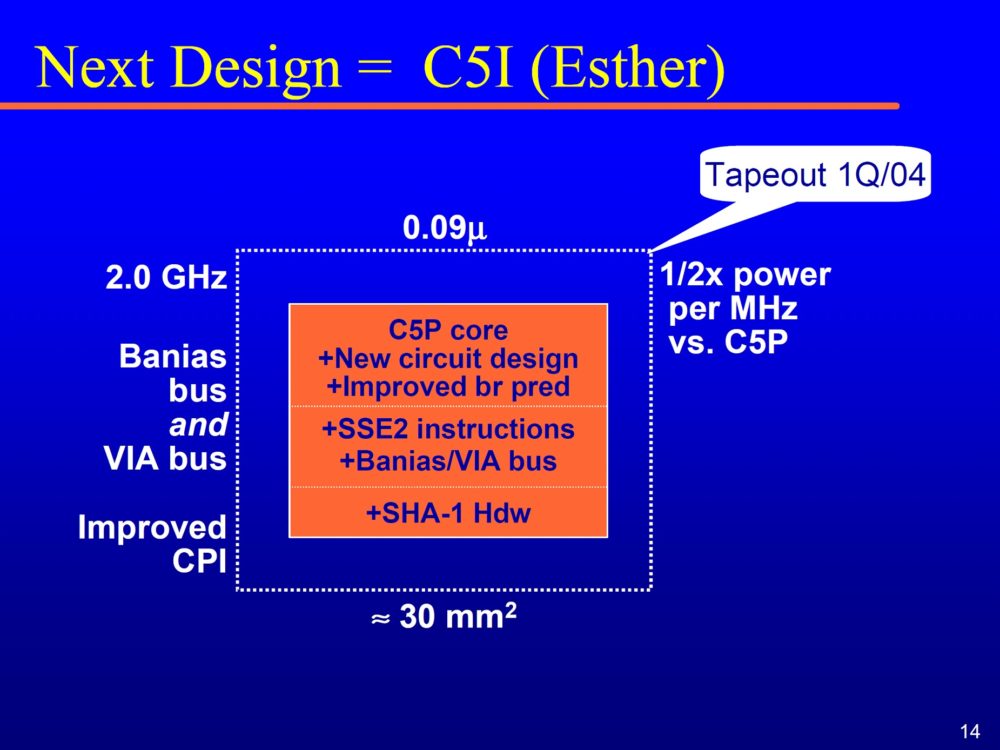

0.18µm 製程、支援 SSE2 的 C5Z 跑到哪裡去了?這個硬體 SHA-1 密碼雜湊演算法的 C5I 又是從哪邊跑出來的?

2004 年:由「倖存者」C5P 為出發點,重新開展的時程表。

但這時候威盛 x86 處理器的時程表,總算有了一貫的邏輯(儘管維持雙重核心代號):從 Pentium III 「Tualatin」匯流排移轉到相容 Intel Socket 479 腳位,但電器信號改用自家規格以避免侵權,並在通訊協定層面稍做改進(如資料寫入效率)的 VIA V4 Bus。

細心的讀者一定會留意到:C5P 的規格又被偷偷的小改了。

2004 年 5 月 18 日公開 C5J 產品代號、2004 年 9 月 17 日公布 VIA C7 品牌、到 2005 年 5 月 27 日產品上市,C5J 算是歷經 4 年的集大成之作,從製程、時脈、快取、指令集、匯流排、資安硬體功能到多處理器,在每個環節都有重大的躍進。

靠著 IBM 的 0.09µm 製程,C5J 晶片竟然縮小到 31.7 mm²,僅為 WinChip 2(95 mm²)的三分之一,Glenn Henry 這個人與其領導的 Centaur 團隊,對於壓低成本的執念之深,讓人感到恐怖。也許把產品「cost down」到看起來很玲瓏精巧,就是他們工作成就感的來源。

「幾乎 Tape Out」的 C5I(被 C5J 取代),和 C5Q(台積電 0.13µm)、C5R(台積電 0.11µm)與 C5W(IBM 0.09µm 改良版),也就默默消逝在簡報的盡頭。

走過風風雨雨的 4 年,這麼多的 Centaur 產品代號,扣除早期的 C5A/B/C,僅 C5N、C5XL、C5P 和 C5J 撐到量產上市的那一天。

很巧的是,這段期間,也正是 Intel 以威盛未得其同意,擅自銷售 Pentium 4 處理器相關晶片組為由,對其發動官司訴訟大戰,並糾纏了近 3 年。這場法律戰的影響,與是否就是產品開發計畫東改西改的主因,外人就不得而知了。

但唯一可以肯定的是:威盛和 Centaur 對「降低成本」的堅定信仰,如同信奉宗教般的虔誠。天真的相信,只要東西做得夠便宜,就一樣會有人願意買單,又偏偏是不少台灣企業(或許可加上某些美國人)的通病。

最終不得不與魔鬼進行交易

俗語說的好:出來混的,總是要還。多年來死守「成本至上」信條、堅決抗拒高效能處理器主流技術趨勢的 Centaur,終究得面對效能競爭力遠遠不如對手的殘酷現實(到了 2005 年,還沒有超純量管線,距離 Intel Pentium 已 12 年),64 位元的普及速度超乎眾多 x86 處理器小廠的預期(Transmeta 對此應該很有感),更是需要盡快提供解決方案的重點項目。

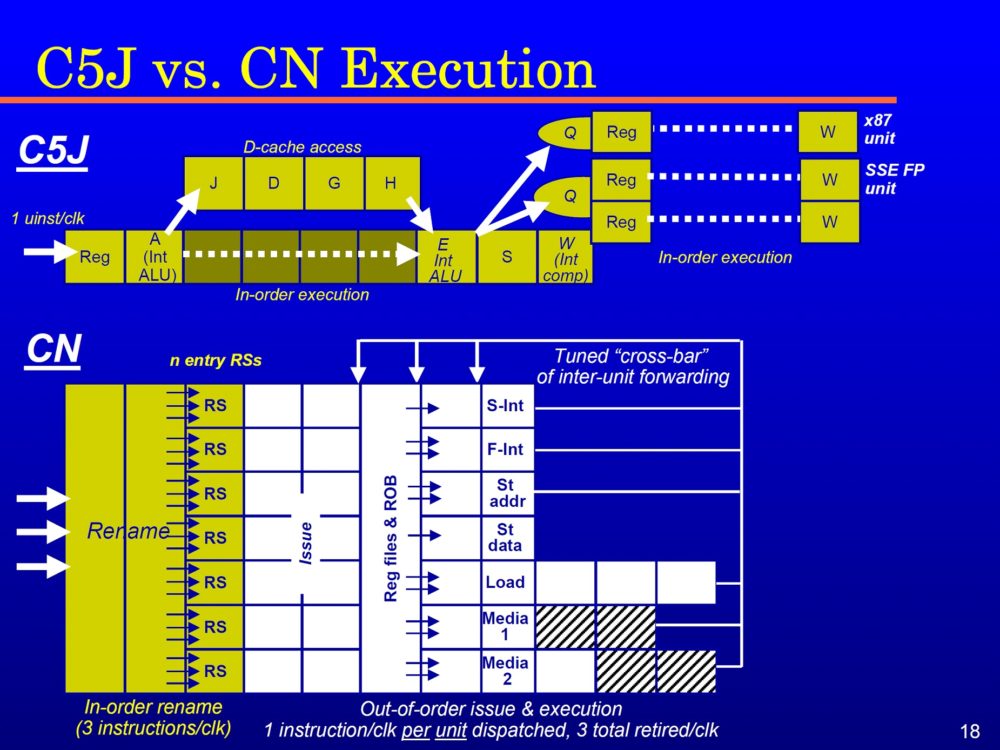

在 2004 年 10 月 5 日,跟隨著 C5J(VIA C7)一同曝光的「全新下一代微架構」CN,很明確的昭告天下:Centaur 還是得擁抱超純量管線、「魔鬼的工作」非循序指令執行、預測執行(結合動態分支預測和非循序指令執行),以及 64 位元和更高效率的多媒體應用效能。當然,在任何可以想到的環節,也勢必要有足夠的進化,才有可能跟得上 x86 雙雄的腳步──最起碼拉近那巨大的差距。

令人感到好奇的是:「面面俱到」的 CN,其產品開發時程,還能夠像過去的 Centaur 產品,一樣的神速嗎?還有辦法在兩年之內,也就是在 2006 年就推出產品嗎?

筆者只知道:從公司創立以來,微處理器報導(Microprocessor Report)舉辦的活動,幾乎無役不與的 Centuar 與其看板人物 Glenn Henry,從 2005 年到 2007 年,就再也沒站上這些活動的演講台了。

等待了整整 3 年,2008 年 1 月 23 日,威盛公開代號 Isaiah 的新世代 x86 處理器微架構,3 月開始大量提供樣品給客戶,5 月 29 日正式命名為 Nano(凌瓏)處理器系列。其腳位與 C7 相容,因此廠商與客戶可用較低的成本升級產品,也同步推出超低電壓的低功耗版本。

再來就是一連串事件發生時間與我們越來越近的故事。

2009 年 11 月 3 日,從富士通 65nm 製程轉進至台積電 40nm 製程的 Nano 3000 系列,開始支援 SSE4.1 指令集,並修正「殘廢」的第二個整數運算單元,使其可執行大多數整數運算指令。

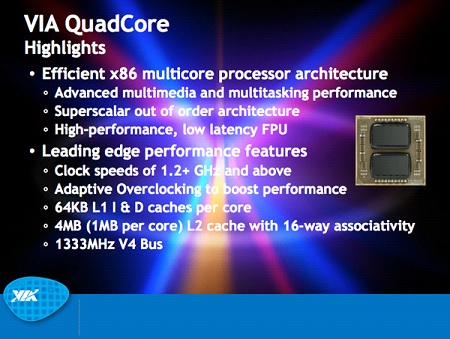

2011 年 5 月 5 日,台積電 40nm 製程 Nano X2 邁進原生雙核心。

2011 年第三季末,四核心(兩顆雙核心封裝成單一晶片)正式出貨。

2014 年夏季,台積電 28nm 製程、時脈 2GHz 的「Isaiah II」樣品與測試數據曝光,支援 SSE4.2、AVX 與 AVX2 指令集。

但卻也被人發現:在某些 SPEC CPU 的效能測試項目,編譯程式時啟動 AVX / AVX2 時,效能不增反減,推測跟實作 AVX / AVX2 的手段有關,很可能只是透過修正微碼實現相容性,但處理器微架構層面卻毫無任何配套措施(Intel 和 AMD 都為此下足功夫),無愧 Centaur 那套「簡單、迅速、便宜」的最高指導原則。

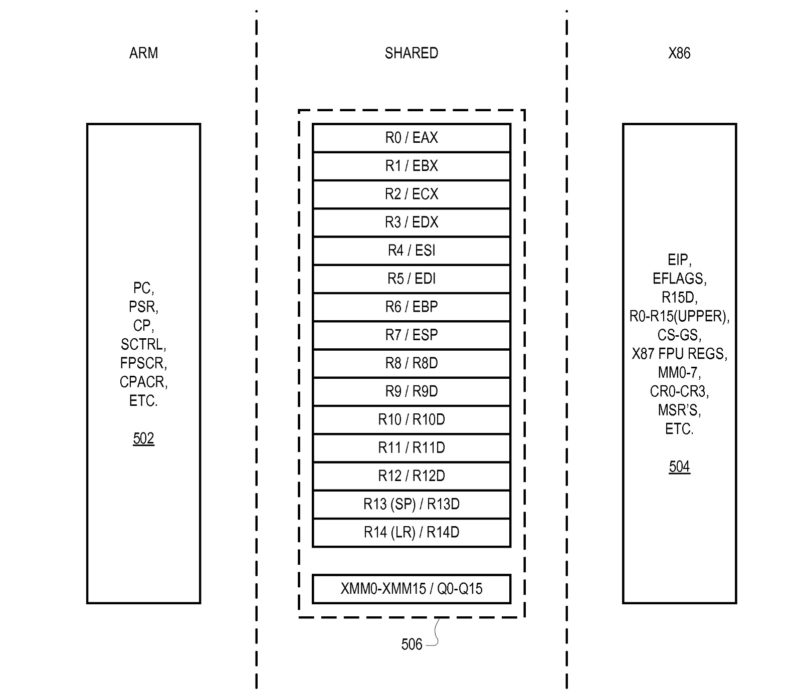

有趣的是,那時有人注意到,威盛有份「疑似打造 x86 / ARM 混合架構處理器」的專利,也剛好是 AMD 剛宣布將融合 x86 與 ARM 的系統架構,並研發 K12 處理器的「簡報王」時期,讓人不聯想到威盛想趁機跑去湊熱鬧的念頭。最後,無論是AMD和威盛,這偉大的創舉,從來就沒有成真。

總之,各位可以回憶一下,在任何威盛推出新品的時間點,Intel 和 AMD 擺在市場上的是哪些產品,又是怎樣的製程和規格,又是何等規模的性能與出貨。然後威盛與 x86 雙雄的差距,就這樣越拉越遠。基本上,說威盛早就看不到那兩家的車尾燈,恐怕也不會有太多人會「膽敢」反對。

至於威盛這間公司為何從叱吒風雲的台灣股王,走向極盛而衰,到近幾年面臨下市危機的慘況,在過去早已是無數財經媒體的封面故事,就不在本文的探討範圍,也沒有特別為此大書特書的必要了。筆者只記得十幾年前,威盛某高層曾豪情萬丈的公開喊話:在嵌入式應用的市場,沒有 AMD 的份。

難道威盛和 Centaur 的 x86 處理器,除了低價位的嵌入式應用整合方案外(其實威盛握有的武器是很完備的),就沒有其他的出路嗎?2019 年 11 月 18 日的新聞稿,倒是提醒了世人,他們並未坐以待斃,寄望從人工智慧的推論應用,找出一條生路,甚至還有機會從 5G 時代的多接取邊緣運算平台(MEC),切入伺服器市場。

目標「人工智慧推論伺服器」的 CHA

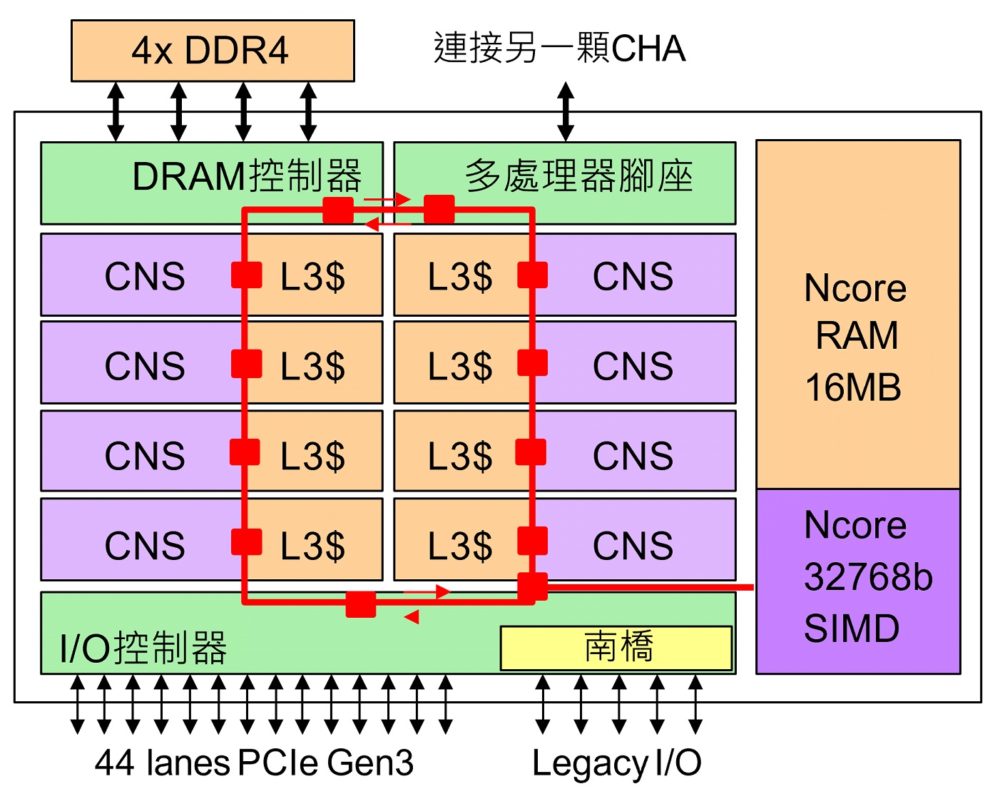

在 2019 年 11 月 18 日亮相的 CHA 系統單晶片,整合了 8 個 CNS 處理器核心、16MB 第三階快取記憶體、4 通道 DDR4 記憶體控制器、44 Lane PCIe Gen3、Ncore 人工智慧輔助處理器,並可雙處理器組態,2020 年下半年量產,這是自從 Nano 之後,睽違超過十年的全新設計。CNS 採用台積電 16nm 製程,晶片面積是「破天荒」的 195 mm²,標準設計功耗不高於 85W。而此時此刻,Glenn Henry 則已經是半退休狀態了。

Centaur 宣稱 CNS 是「Intel Haswell」等級的微架構,從環狀架構(Ring)處理器內部匯流排也看得出 Sandy Bridge 到 Broadwell 的影子(之後的 Skylake 就轉向更有效率的 Mesh 匯流排),但 22nm 製程的 Haswell 卻早在 2013 年 6 月 4 日就已出現,技術整整落後超過 6 年的 CNS,論處理器核心的效能,根本一點拼面都沒有。若無讓人眼睛一亮的新兵器,連能否打得過 Intel「瞄準 5G 基地台商機」的 24 核 Atom 處理器,都是天大的問號。

所以除了連 AMD Zen2 都尚未支援的 AVX-512 指令集(雖然內部拆成兩個 256 位元運算微指令,實際效能有所疑慮),就是從 5 年前開始熱門的「人工智慧處理器」下手了。

CHA 的產品定位,很明顯的鎖定 5G 時代的邊緣伺服器,如 ETSI NFV 架構的多接取邊緣運算(Multi-access Edge Computing,MEC),或工業物聯網的網關(Gateway)。較「古老」的 16nm 製程,大概可提高 CHA 對惡劣運作環境的防禦力。而根據「人工智慧即將無所不在」的教條,這些應用或多或少用得到推論功能(像人臉辨識之類的)。威盛想踏入高獲利的伺服器市場,意圖不言可喻,但 CHA 值多少價格,那又是另一回事了。

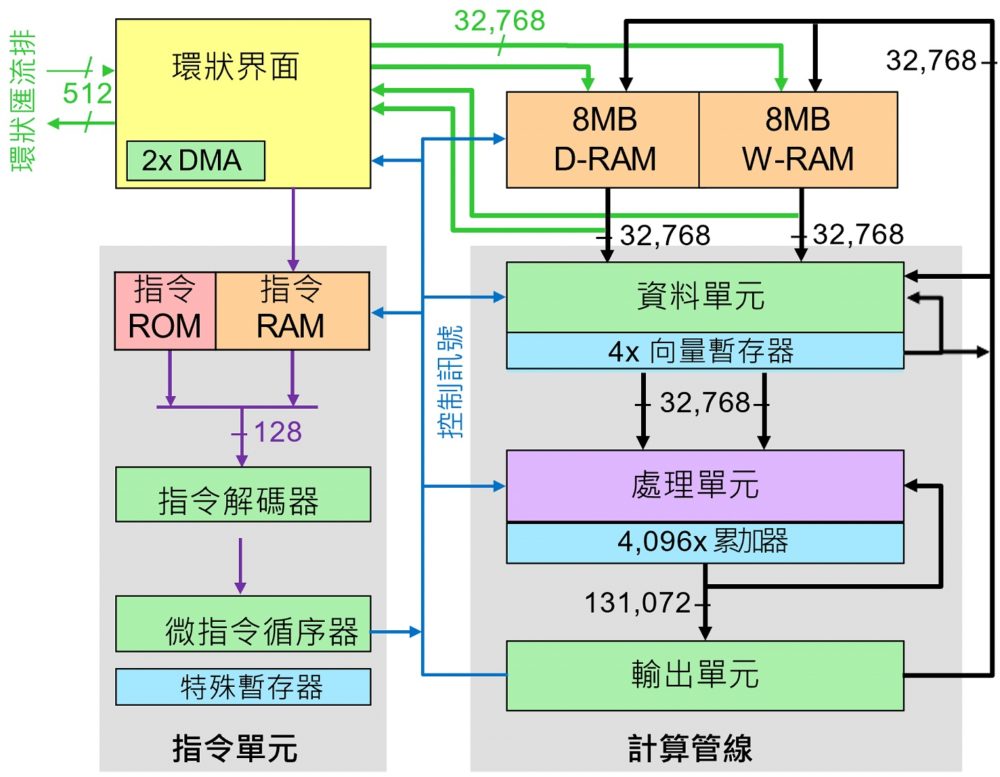

由 Glenn Henry 親自操刀的 Ncore 人工智慧輔助處理器,晶片面積 34.4 mm²(恰巧是他非常熟悉的尺寸),採用超寬的 32768 位元 SIMD 架構,藉由理論值 20TB/s 的 16MB SRAM 挹注充沛的記憶體頻寬,當執行推論常用的 INT8 短整數時,擁有每秒 20 兆(20T/s)的最高運算能量。Ncore 亦可支援在深度學習開始普及的 Bfloat16 浮點數,但峰值效能會只剩下 INT8 三分之一。

這看起來好像很了不起,但這性能究竟如何,可以參考一下 Google 的第一代 TPU(2016 年):INT8 最高效能約 92T/s。換句話說,Ncore 連其四分之一都不到,大致上跟 Pascal 架構(2016 年)的 nVidia Tesla P4 相去無幾(22T/s)。同場加映 Turing 架構(2018 年)的 nVidia Quadro RTX8000 是 261T/s,推論專用的 T4 則是 130T/s。

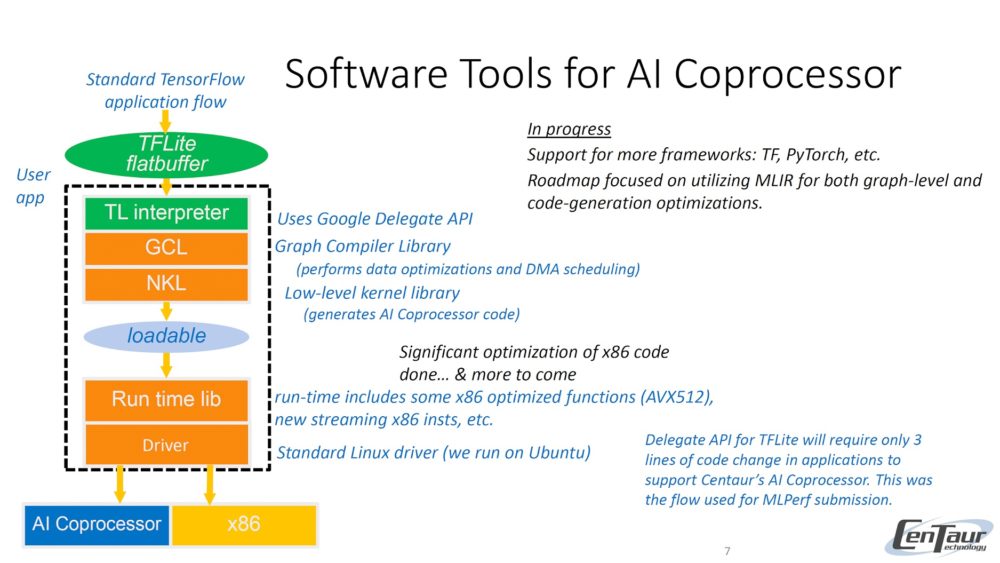

當然,你也可以認定這個 Ncore 是「免費附贈」的,效能單位成本與「效能 / 功耗比」,可能遠優於現有市場上的其他方案,無需外掛運算加速卡也是顯而易見的優勢。但對於人工智慧應用,因為「硬體製造商和軟體開發者」之間的鴻溝實在太深(像 Google 這樣自產自用 TPU,反而就沒這樣的困擾),意思就是這票技術先驅者做出來的硬體,不是不好用就是不合用,導致 5 年前吸引眾多有志之士一窩蜂湧入的人工智慧晶片熱潮,正在急速退燒中。

威盛和 Centaur 是否能夠提供滿足軟體開發者的完整解決方案,避免重蹈覆轍,犯下無數「先賢先烈」的過往錯誤,將決定壓寶人工智慧這個決定的成敗,否則,CHA 將淪為「即不簡單,更不迅速,只能便宜」的低價產品。

唯偏執狂得以倖存,但卻不會帶來成功

「唯偏執狂得以倖存」(Only the Paranoid Survive),是Intel創辦人之一的安迪‧葛洛夫(Andy Grove)的傳世名言,一語道盡他戰戰兢兢、戒慎恐懼經營 Intel 的心路歷程。但我們也很清楚,Intel 之所以會如此成功,也不是只靠偏執而已。Centaur 偏執於「簡單、迅速、便宜」的理想之路,卻是另一個極端的反例。

他們的確靠著死守著最低成本的堅持,成為 Intel AMD 之外,唯二還念得出名號的 x86 處理器廠商(另一間是俄羅斯的 Elbrus),但這些產品是否帶來商業上的成功,相信各位心中自有定見。也許威盛並未供給 Centaur 足夠的經費和人員,也施加極度嚴苛的成本要求,在 Time To Market 的前提下,難以完成更先進產品的開發。

這些年來,Centaur 也很可能存活得很艱辛,朝不保夕,箇中甘苦,不足外人道也。但不幸的是,市場和消費者並不會理會這些「藉口」,他們只會在意產品能不能讓他們感到滿意。

不計代價的把東西做到價格最低廉,就絕對會有人樂意接受?這世界的運作,從來就不是這麼的簡單,沒有永恆不變、放諸四海而階皆準的準則。或許,這就是堅守「簡單、迅速、便宜」的 Centaur 和威盛 x86 處理器發展史,帶給我們的教訓。

(首圖來源:VIA Gallery / CC BY)

"技術" - Google 新聞

May 10, 2020 at 12:07PM

https://ift.tt/2LgbddP

台灣處理器拾遺》成為威盛電子x86 處理器技術基礎的Centaur(下) - 科技新報 TechNews

"技術" - Google 新聞

https://ift.tt/2vdsyzX

Shoes Man Tutorial

Pos News Update

Meme Update

Korean Entertainment News

Japan News Update

Bagikan Berita Ini

0 Response to "台灣處理器拾遺》成為威盛電子x86 處理器技術基礎的Centaur(下) - 科技新報 TechNews"

Post a Comment